Optical probes for wafel-level testing and co-packaged optics

Keystone Photonics is now a part of FormFactor. Learn more

Product Range

Custom Optics

|

Lens with high NA for die-level laser and PIC testing. |

|

Lens with low NA for die-level spot-size converter testing. |

|

Large working-distance for wafer-level testing of grating couplers with well-defined best coupling position. |

|

Collimated output with up to 30 μm MFD for coupling to other lensed devices. |

|

Asymmetric lenses with 0° to 20° deflection. |

|

90° deflection for wafer-level testing of edge-coupling devices in 100 μm trenches. |

|

Large working-distance for extra clearance. |

|

85° emission for better top-view camera vision. Other angles available upon request. |

|

More options and design&simulation service available upon request. E.g. cryo compatible, extended wavelength range, anamorphic lens designs, metal-coated optics etc. |

Fiber Arrays

|

Fiber arrays up to 64 channels |

|

Lensed fiber arrays for both die and wafer level testing of angled facets (e.g. InP laser, SOA, SLED). |

|

Any pitch, fiber type, mixed fiber arrays, PM fiber arrays, cryo, UV, VIS NIR fiber arrays are available upon request. Every channel of a fiber array can be equipped with different optics. |

|

Range of 3D-printed markers for top- and bottom-view camera alignment. Suitable for surface and trench coupling. |

|

Photonic integrated circuits (PIC) can be used as a means for pitch equalization or pitch reduction to 20 µm. Such probe heads allow testing of ultra-low pitch photonic integrated circuits both using grating and edge-coupled devices. PIC may be equipped with 3D-printed mirror optics or a straight lens.

|

Custom Fiber Array Mounting

|

|

Test & Validation

|

|

Optional mode-field and transmission measurements. |

Request Form for Standard Products

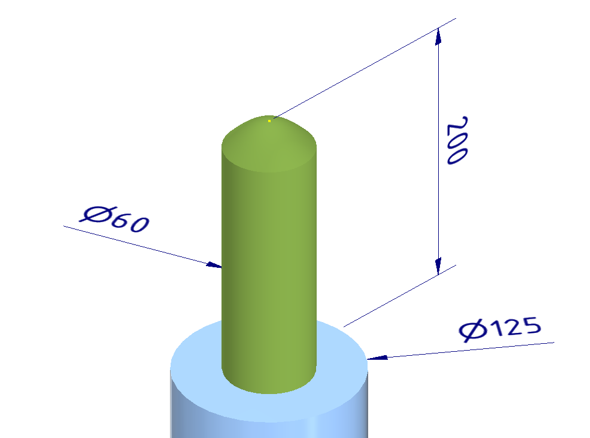

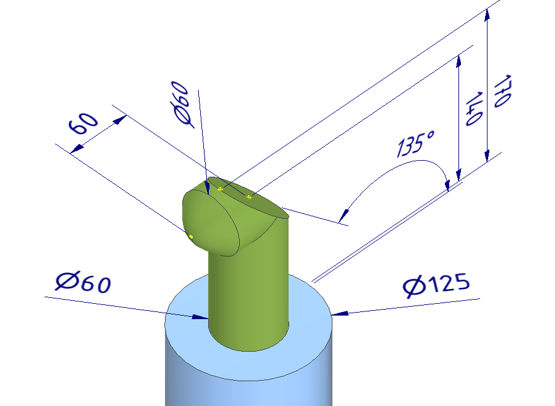

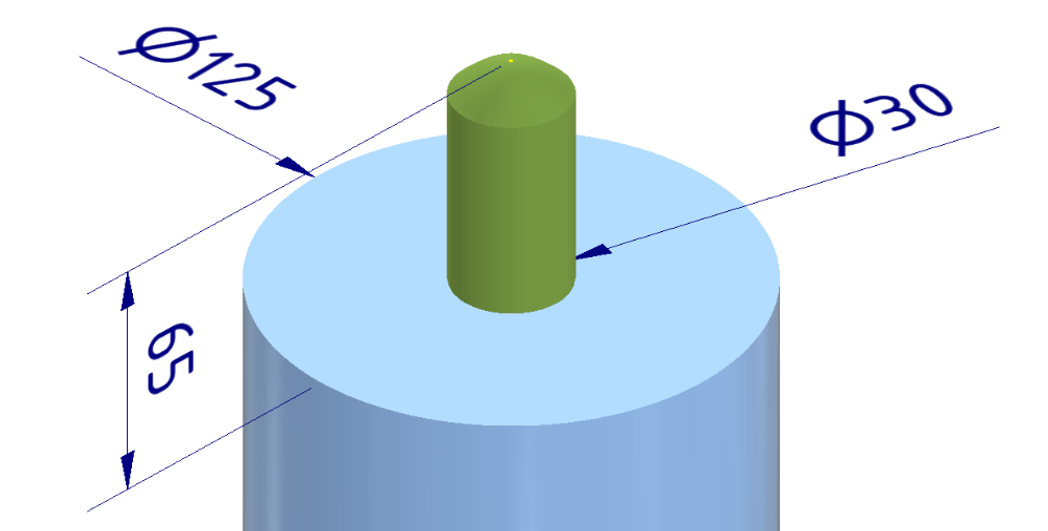

Standard Corpus Types (µm)

Corpus type A

Corpus type B

Corpus type C

Corpus type D

Optional markers compatible with commercial probe stations

- All calculations were done with Gaussian approximation

- All MFD are specified at 1/e² intensity level

- MFDs correspond to UHNA4 and SMF28 fiber (except for smallest MFD)

- WD is measured from apex of lens to waist

- Measured coupling efficiency is pending, estimated coupling is 0.5 dB for large MFD,

1 dB for smallest MFD, TIR surface has 0.1-0.3 dB penalty

Our Technology in a Nutshell

Keystone Photonics‘ Wafer-Level Testing at ‚Optica Online Industry Meeting: PIC Packaging for Volume Production‘

Publications

Wafer-Level Testing for Photonic Devices

At Keystone Photonics, we closely follow emerging innovations that align with our mission to push the boundaries of photonic integration and test solutions. A recent article in the September–October 2025 issue of Chip Scale Review highlights just how transformative micro-optics have become for the future of AI hardware scaling and semiconductor testing.

The report underscores micro-optics as a key enabling technology, offering an order-of-magnitude improvement over conventional approaches across a wide spectrum of industrial and research applications. Among the key innovations discussed:

- Scalable optical probes supporting 64+ channels for high-density optical I/O testing

- Automated alignment and calibration features, reducing setup complexity and operator dependence

- Ultra-fine pitch arrays capable of probing devices with 20μm pitch, supporting next-gen chip architectures

- Smart probes with integrated distance sensors to prevent wafer damage and improve throughput

These advancements are further enhanced by seamless integration into wafer-level testing setups, using standardized mechanical interfaces and auto-alignment capabilities.

Importantly, the technology supports double-sided wafer testing and finally opens the door to CPO testing.

We invite you to explore how our technology can support your next-generation optical test and packaging challenges.

Read the full article here: Wafer-level testing of photonic devices – Chip Scale Review, Sept–Oct 2025

Authors: Philipp Dietrich, Andrés Machado, Florian Rupp, Roman Zvahelskyi